在之前的5篇文章中,我们简要的分析了SATA协议的内容,可以看出来,对比并口硬盘所使用的PATA协议,SATA技术比较复杂,数据处理的环节多,处理方式多样。

以前,用8位的单片机,通过使用2个port口的方式,就可以用PIO的方式读写IDE硬盘了。但是对于SATA硬盘,就不能用这种方法了,高速串行信号呀,1.5Gbps、3.0Gbps、6.0Gbps,速度太快了,想想CPU才多快。那么对于这么高的速度,怎么样实现对SATA硬盘的脱机读写呢?一种方法是设计ASIC,这个成本太高,性价比太差。一种方法是用SATA转PATA的桥,比如Marvell的和JMicro的桥接芯片,优点是简单,缺点是速度不快,你想PATA最高才133MB/s,而SATA最低也能150MB/s呢。那么性价比最好的方法来了,就是用FPGA来实现SATA接口,FPGA作为Host端,SATA硬盘作为Device端,脱机读写SATA硬盘。

FPGA作为一种通用的芯片,处理这种高速接口还是得心应手的,千兆以太网、FC、PCIE都不在话下。目前高端的FPGA,都集成了高速收发器GTP、GTX等,利用这些高速收发器,可以实现SATA的物理层前端。下面,我们就SATA接口的物理层的实现做详细的分析和介绍。

SATA协议物理层使用高速差分信号进行数据传输,支持OOB信号,物理层速率为1.5-6.0Gbps,在FPGA上使用普通I/O无法实现,需要针对设计需求使用特殊的器件。现阶段许多FPGA公司设计的FPGA中带有硬核,用于支持高速串行传输,Xilinx公司的Virtex5系列即是其中的一种,Rocket IO是集成在Virtex5 系列中灵活的、功能可配置的千兆位级串行收/发器,其中LXT系列集成的GTP收发器支持600Mbps~3.125Gbps的数据传输速率,FXT系列集成的GTX收/发器支持 500Mbps~6.5Gbps的数据传输速率,并且Rocket IO支持SATA协议物理层的OOB信号,因此,Rocket IO可以理想的应用于SATA协议物理层的实现。

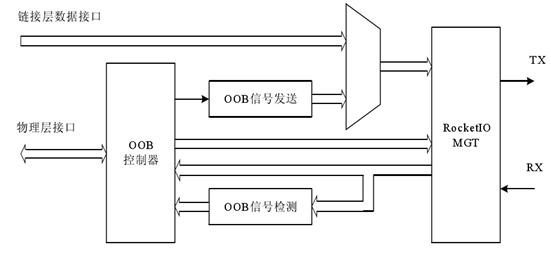

物理层整体结构框图如下图1 所示。主要包括高速串行链路的实现、OOB控制模块两个方面 。可采用Xilinx公司的Virtex-5 FX芯片内部集成的千兆级收发 器Rocked IO MGT 实现 1.5Gbps和3.0Gbps的物理层高速串行通信,提供20bit 宽的并行数据接口。OOB 控制模块通过逻辑状态机实现OOB 信号的检测与发送,实现通信连接的建立。物理层接口模块向链接层提供标准的访问接口。

图1 物理层结构图

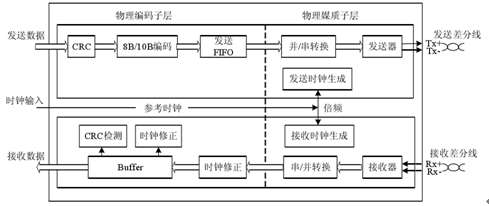

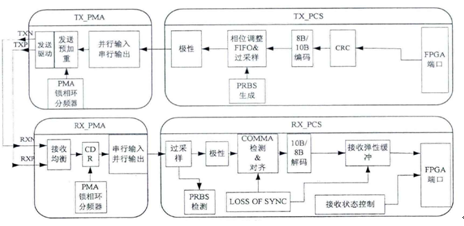

物理层中用到的RocketIO,由物理介质附属子层(PMA)和物理编码子层(PCS)组成。内部主要功能框图见图2、图3,PMA包含串行器/解串器(SERDES)、TX与RX输入/输出缓冲器、时钟发生器和时钟恢复电路。PCS包含8B/10B编码器 /解码器、扰码器/解扰器以及支持通道绑定和时钟校正的弹性缓冲器。

图2 RocketIO内部结构1

图3图2 RocketIO内部结构2

完整的GTP_DUAL由GTP0和GTP1组成,以上仅为GTP0的结构。GTP1与其相同,中间共享时钟复位等模块以节省面积和功耗。上为发送端下为接收端,未与硬盘连接时可进行内部测试,如虚线所示。把发送差分端口连至接收端,可检验接收端的并行数据与发送端是否一致。

PMA为Physical Media Attachment,指物理介质附属子层,是收发器高速运行的关键器件。内置串并转换模块,串行时钟高达并行时钟的20倍,用锁相环(PLL)实现。由于频率越高,信号衰减越严重,发送预加重和接受均衡用于补偿信号的高频分量来保持信号的完整性。CDR为Clock Data Recovery表示时钟数据恢复电路,采用锁相环技术从串行码流中提取时钟信息。另一部分PCS为Physical Coding Sublayer指物理编码子层,对并行码流进行编码处理。COMMA字符即ALIGN的首字节它包含COMMA序列,即该字符的前七位0011111或1100000,检测该字符有助于识别正确的字节边界。PRBS是伪随机二进制序列,测试数据的误码率。8B/10B编码和CRC校验不在此赘述。全部的功能选项己在图3中标出,可根据系统需求自由配置。

SATA物理链路建立连接过程:

(1)主机上电,由主机发送 COMRESET 信号,用于硬件复位,之后物理链路进入空闲状态;

(2)设备上电,设备接收到COMRESET信号,且检测到物理链路被释放之后发送 COMINIT 信号;

(3)主机接收到COMINIT信号之后首先对接收到的信号去抖,当确认检测到的是 COMINIT信号后,主机发送COMWAKE信号,之后释放链路;

(4)设备在接收到主机发送的COMWAKE信号后,并且在链路空闲情况下,发送 COMWAKE信号;

(5)设备在发送COMWAKE信号之后,以支持的最高速度发送ALIGNp原语,之后设备开始等待主机发送的ALIGNp原语;

(6)主机检测到设备发送的COMWAKE信号,且等待总线空闲后,主机开始发送 D10.2字符,等待873.8μs来自设备的ALIGNp原语,在接收到ALIGNp原语后,根据接收到的ALIGNp原语来确定链路速度,之后以确定的速度发送ALIGNp 原语,之后如果接收到来自设备端的3个连续的非ALIGNp原语(以K28.3开头),则链路建立连接,主机开始发送来自链路层的数据,并保持此状态,若主机等待 873.8μs 仍然没有接收到3个非ALIGNp原语,则主机认为当前链路初始化失败,主机重新开始进行链路层初始化;

(7)设备等待来自主机端的ALIGNp原语,当等待54.6μs仍然没有接收到ALIGNp 原语时,设备降低速度模式,重新发送ALIGNp原语,重复执行此操作,直到接收到主机端发送的 ALIGNp原语为止,之后设备开始发送来自链路层的数据,若在最低速度模式下等待54.6μs仍然没有接收到ALIGNp原语,则设备认为当前链路初始化出错,设备端进行错误处理,之后进入空闲态。

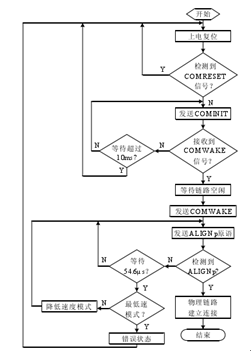

图4 物理层初始化过程

SATA物理链路初始化过程实现:

Xilinx 的FPGA开发工具ISE提供GTP生成向导,可以实现SATA协议物理层定义的功能,由于FPGA上有丰富的存储资源,对OOB信号的发送采用预先把ALIGN 固化在存储器中,然后控制存储器的读时间和间隔时间来完成。因此,使用 FPGA 实现 SATA协议物理层最主要的工作在于设计联合逻辑,控制GTP完成 SATA协议初始化功能,设计SATA协议初始化流程图如图5所示。

初始化过程需要严格按照协议规定,与主机端协同完成。设备端在上电之后首先检测 COMRESET 信号,当检测到 COMRESET 信号后,并且链路空闲时,发送 COMINIT 信号,并等待主机端应答,当超过10ms 仍然未接收到主机端应答时,设备重新回到上电复位状态,若在10ms内检测到主机发送的COMWAKE信号,且等待主机释放发送信号线后,设备对主机发起COMWAKE信号,之后设备以支持的最高速率发送同步原语ALIGNp,之后等待主机返回ALIGNp原语,若在54.6μs 内都没有检测到主机发送的ALIGNp原语,则设备进入降低模式状态,降低传输速率,若当前传输模式即为最低传输模式,则设备初始化失败,处理错误并返回上电复位状态,若当前设备不是最低传输模式,则设备降低速率,重新开始发送 ALIGNp 原语,当检测到主机发送的ALIGNp原语时,设备与主机间的链路建立连接,SATA物理链路初始化成功,然后可以开始进行数据帧的交互。

图5 SATA物理层初始化流程图

选用 Rocket IO GTP作为SATA协议物理层高速串行数据收/发器,可以简化SATA物理层的设计过程。通过分析SATA协议物理层链路建立连接过程,可以设计OOB信号控制状态机,采用FPGA控制Rocket IO GTP完成SATA协议初始化功能,实现SATA物理层的功能。

总之,SATA物理层的实现,就是配置好GTP和设计OOB信号处理状态机这两个关键点,处理好这两点就可以实现SATA接口的物理层。后续文章中将陆续介绍SATA的链路层、传输层、命令层和应用层的实现方法和技巧。

关于达思科技

达思科技,国家级高新技术企业,天津市国家保密局涉密载体数据恢复唯一协作单位,数据恢复和取证行业著名品牌,是一家以技术研发为核心生产力的技术型企业,在国内乃至全亚洲数据恢复与取证技术领先!

达思科技 中国数据恢复与取证专家!热线:4007000017

更多数据恢复与取证技术、互联网请关注微信公众订阅号:woocs

微信号:woocs

长按识别二维码关注

专注数据恢复与取证技术、互联网

电话咨询:400-700-0017

投稿:woocs@qq.com

达思北京数据恢复中心(全国总部)

数据恢复服务咨询:400-700-0017

数据恢复培训咨询:010-62672120

达思数据恢复软件:010-62672120

达思软件技术支持:010-62672120

达思总部

数据恢复实验室: 010-62672120

数据恢复实训室: 010-62672120

电子取证实验室: 18600668588

软件销售QQ:

55356052

55356052远程协助QQ:

65196945

65196945邮件联系:sos@dstchina.cn

邮件支持:support@dstchina.cn

24小时免费电话:400-700-0017

24小时监督电话:18600668588